# MANAGING COMPLEXITY IN MACHINE VISION.

TKH Vision with its member companies offers a huge portfolio of products, technologies and competences. We as TKH Vision have almost every technology available that is needed setting up vision systems for 2D and 3D applications. With our product and competence portfolio we will find, together with our customers, the right answer in nearly any case.

Our customers are challenged every day by the variety and complexity of vision technologies. The decision about the right products, data processing algorithms and the best combination of suitable technologies is a challenging task that requires extensive know-how. In many cases of-the-shelf products or the combination of those do not fulfill all requirements to the fullest satisfaction. Many vision applications require even more specific attention, especially if it comes to demanding environments, narrow available space, integrated data analysis in combination with a series proof, robust design that withstands 24/7 requirements and is easy to service.

The TKH Vision Solution Center takes care of any application requirement and provides integrated, turnkey vision solutions for machine builders and integrators. In close cooperation, we manage machine vision complexity of our customers worldwide and develop unique serial production solutions that are perfectly designed to fit the application requirements.

The TKH Vision Solution Center is located in Konstanz/Germany and is powered by Chromasens GmbH where more than 40 engineers create individual vision solutions since more than 20 years.

Alexander van der Lof CEO of TKH Group Mark Radford CEO of LMI Technologies, Vice President of TKH Vision

Martin Hund CEO of Chromasens GmbH and TKH Vision Solution Center

### **APPLICATIONS**

The variety of vision applications is almost unlimited. With hundreds of man years of design experience our engineers solve the applications of our customers and provide specialized, integrated vision solutions that we produce in series, 100% tested.

Based on detailed discussions with our customers we understand the applications of our customers and develop unique solutions. We have extensive know-how in all engineering sciences to offer hardware and software imaging processing solutions that meet all requirements and serve our customers' needs in all applications. No matter if we are dealing with outdoor or clean-room requirements.

We support area-scan and line-scan vision in 2D and 3D, deep-UV, UV, visible, IR, NIR and SWIR spectral range.

Our customers are market leaders that require stable serial solutions, engineered according to their specific application requirements. Vision solutions have a wide set of requirements. We convert customer requirements into technical specifications and design turnkey products that we deliver in series.

The TKH Vision Solution Center solves application requirements with its own scientists and engineers in a well-structured approach. In many cases, the solution process requires first a phase in which feasibility must be verified.

In our specialised laboratories with experienced application engineers we carry out feasibility studies for our customers and convert the result into technical specifications of hardware set-ups and processing of image data. Based on the technical specifications, we start the engineering phase, design prototypes and finally produce in series.

### FROM THE IDEA TO THE PRODUCT

For our customers, we take care of all aspects: functionality, design space, production quality, supply chain, service and repair.

The TKH Vision Solution Center serves the customer throughout the entire lifecycle in a true partnership as an industrial experienced, reliable and proven expert.

# ENGINEERING AT TKH VISION SOLUTION CENTER

The TKH Vision Solution Center has extensive scientific and engineering capabilities that enable the design of leading-edge vision solutions for our customers. With dedicated program managers we serve our customers as one-stop shop from first discussions and feasibility analysis to the design of a of a specific solution until serial deliveries.

We understand physics - and design light sources for various industries since more than 30 years. With our sophisticated LED drivers we also support stabilized multi-spectral and strobe light applications.

1111

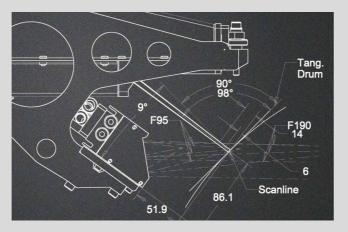

If needed, our experts simulate via ZEMAX to a maximum detail the optic/light designs to achieve the best price-performance ratio. We enable full-custom lenses with even better price-performance ratio where required.

With beam-splitters, prisms, mirrors and integrated thermal management we enable most compact and ruggedized vision solutions that make these sub-systems easy to integrate.

### VISION TECHNOLOGIES

The unique TKH Vision product and competence portfolio is the core for our vision solutions. We address applications from deep-UV to SWIR spectral range and we support any sensor resolution and speed. We enable fully synchronized multicamera systems including super-resolution technologies.

The TKH Solution Center also offers services for the most challenging applications, where, for example, accurate factory calibration plays a key role. The many years of experience in the field of colour and geometric calibrations and the effective deployment of calibration and correction algorithms come here into play.

The variety of machine vision applications is huge. Depending on the application we integrate line-scan and area-scan cameras as well as a variety of 3D imaging sensors. We are powered by our TKH Vision members Allied Vision, Chromasens, Mikrotron, SVS-Vistek, LMI, Nerian, NET and Tattile.

To adapt a vision solution to the customer's environment, we support with necessary electronic design competences.

The flexibility ranges from hardware interface modifications and driver development to custom FPGA / GPU / SoC-based data processing implementations. Especially use cases that require a real-time feedback loop benefit from our extensive experience in FPGA based accelerated data processing algorithms.

Moreover, fully customised camera designs are possible if the available portfolio does not yet address the application requirements.

#### ELECTRONIC-/EMBEDDED SYSTEM ENGINEERING

| 🔓 cik                    | 0       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 nreset                | 1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 📑 instr[31:0]            | 010100  | (00000000) (3c) (34) (34) (34) (a0) (a0 |

| 10                       |         | المتصادية وتصادية وتصادين فستصلح تصاديها                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 🔓 dk_wr                  | 0       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 🔓 dk_rd                  | 0       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ▶ 📷 dk_d[7:0]            | 1       | Z X H X e X I X o X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ▶ 🛃 dk_a[4:0]            | 00000   | 00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DEBUG                    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MEMORY                   |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ▶ 📑 mem_addr[31:0]       | 000000  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ▶ 🛃 mem_d[31:0]          | 222222  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ▶ 🛃 nram_we[3:0]         | 1111    | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 🔓 nmem_oe                | 1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| REGISTER                 |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| instr15_11_to_reg_adr_wr | 1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| instr20_16_to_reg_adr_wr | 1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ▶ 🛃 reg_adr_a[4:0]       | z       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ▶ 🛃 reg_adr_b[4:0]       | 0       | 0 %1 (0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 🕨 🛃 regbank[0:31]        | [00000] | <pre>(000000</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| reg_in_d[31:0]           | 000000  | 000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ▶ 📲 reg_out_d_a[31:0]    | 222222  | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| reg_out_d_b[31:0]        | 000000  | 00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 🕨 📑 en_wr_b[3:0]         | 0000    | 0000 0001 00 0001 00 0001 00 0001 00 0001 00 0001 00 0001 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 🔓 en_reg_wr              | 1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### MECHANICAL ENGINEERING

Opto-mechanical design is the key element to a successful system integration. According to customers' requirements we develop opto-mechanical designs that integrate functionalities to make the final solution easy to handle, optimized for cost, 100% tested, fully calibrated and robust. Into one single vision module we integrate functional parts such as lenses, mirrors, prisms, camera electronics, processing electronics, power supply, LED drivers and more.

As part of the engineering process, we discuss with our customers the required optical performance, available design space, target quantities and related manufacturing processes, calibration procedures, thermal management and in field service requirements. System designs that take into account IP protection classes and related environmental certifications guarantee robust systems that will last for many years, even under very harsh conditions.

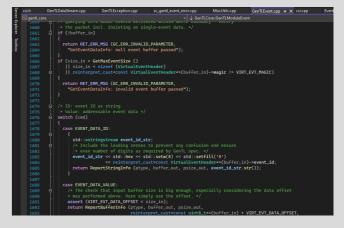

The TKH Vision Solution Center offers comprehensive capabilities for data processing algorithms design and software development. The team implements the initial design of the entire data processing pipeline, as well as fully customised and professional data processing libraries as a solid backend for challenging vision applications.

Depending on the use case and associated requirements, the software can be optimised for CPU or accelerated by GPUs. We use state-of-the-art tools and programming languages for prototyping and efficient deployment for the best (OS-independent) performance.

#### SOFTWARE

We have been developing OEM/full-custom vision systems with proven and robust stability in Konstanz for more than 30 years. 24/7 operation is standard and life-cycle management is a must for all our customers.

Our program and multi-project management team is powered by their strong experience in leading customization projects in the fields of hardware and software development. Agile and classical approaches are used to perfectly fit the project related process requirements – delivering outstanding vision solutions within given schedule and budget. All our business processes are ISO 9001 certified.

The world's biggest brands rely on our expertise in developing and delivering unique innovative and best-in-class machine vision systems that make our engineering customers global leaders.

With our customers, solution partners, various third-parties and universities, we are able to manage complexity in machine vision within a global network.

### LOCATION

We are located in one of the most attractive regions in Germany. In the immediate vicinity of the Swiss Alps and Lake Constance, our teams are inspired by technologies and the environment.

We create unique vision solutions in an open-minded, innovative and multicultural working environment.

Visit us and and get yourself inspired. The TKH Vision Solution Center incorporates a dedicated Experience Center and labs to understand technologies and creatively develop your individual vision solution.

# MANAGING COMPLEXITY IN MACHINE VISION.